# Annexes au Mémoire

présenté par

### Frédéric Desprez

en vue de l'obtention du diplôme

# d'habilitation à diriger des recherches de l'Université Claude Bernard de LYON

(Numéro d'ordre 48-2001)

Spécialité : Informatique

#### **CONTRIBUTION A L'ALGORITHMIQUE PARALLELE**

Calcul numérique : des bibliothèques aux environnements de metacomputing

## Curriculum vitae et articles

Date de soutenance : 20 juillet 2001

Composition du jury :

Rapporteurs Pierre MANNEBACK

Thierry PRIOL

Jean ROMAN

Examinateurs Michel Cosnard

Jack DONGARRA

Thomas LUDWIG

Yves ROBERT

Laboratoire de l'Informatique du Parallélisme UMR 5668 CNRS – ENS Lyon – INRIA Rhône-Alpes.

#### CONTRIBUTION A L'ALGORITHMIQUE PARALLELE

## Calcul numérique : des bibliothèques aux environnements de metacomputing

Annexes: curriculum vitae et articles

#### Frédéric Desprez

#### 20 juillet 2001

Ce document présente quelques unes de mes publications les plus significatives de mon travail depuis la soutenance de ma thèse. L'ordre n'est pas chronologique mais il respecte l'ordre des chapitres du document principal d'habilitation. Les trois premiers articles correspondent au chapitre 2, les deux suivants au chapitre 3 et enfin les deux derniers correspondent au chapitre 4.

#### **Chapitre A Curriculum Vitae**

Je présente mon travail de recherche, d'enseignement et de tâches administratives depuis ma thèse ainsi que toutes mes publications.

#### Chapitre B Optimization of a LU Factorization Routine Using Communication/Computation Overlap

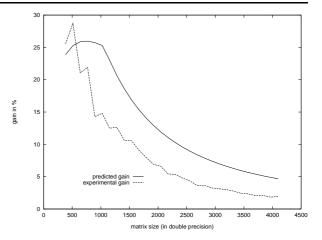

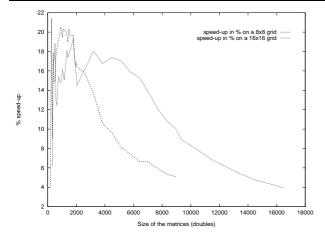

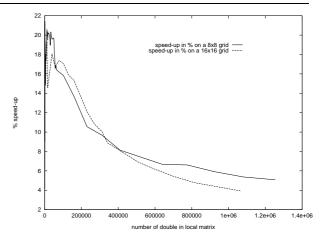

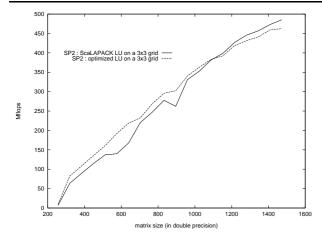

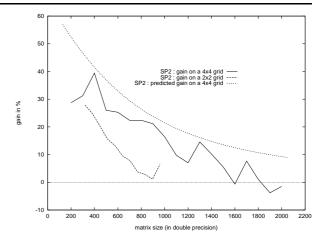

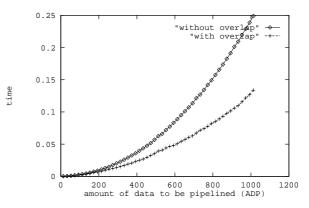

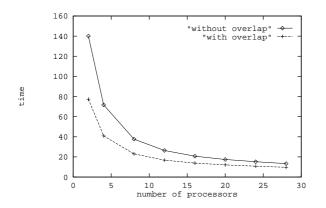

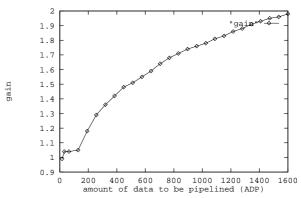

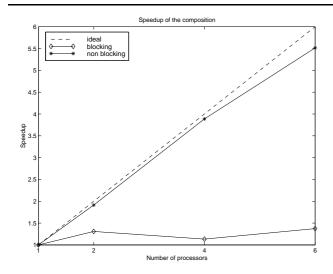

Ce premier article présente mes travaux avec S. Domas et B. Tourancheau sur l'optimisation de la factorisation LU grâce aux recouvrements calculs/communication. Même si les gains ne sont pas très important (20% au maximum), nous avons réussi à les modéliser de manière précise et à tirer un modèle général de cette routine. Ces résultats ont été ensuite réutilisés dans ALASCA pour calculer le coût de calcul des routines afin de trouver les meilleures distributions.

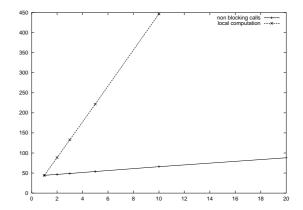

#### Chapitre C Optimal Grain Size Computation for Pipelined Algorithms (1996)

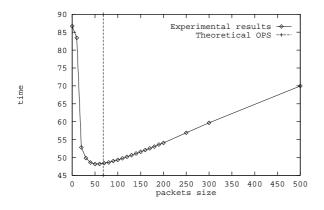

Ces travaux ont été initié durant mon année au LaBRI en collaboration avec P. Ramet et J. Roman. Après avoir étudié durant ma thèse les recouvrements dans des cas linéaires simples, nous avons étendu ces résultats à des polynômes quelconques. Une bibliothèque a été développée qui permet de fournir aux LOCCS la taille de paquets optimale.

## Chapitre D Communications Optimizations and Efficient Load-balancing for a Volume Rendering Algorithm on a Cluster of PCs (2000)

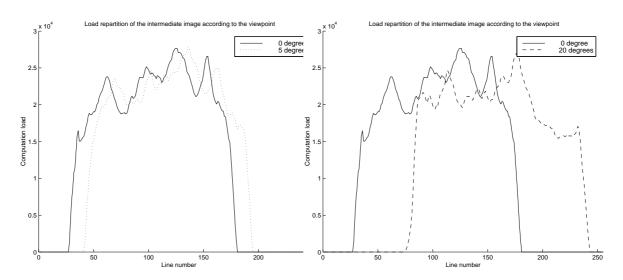

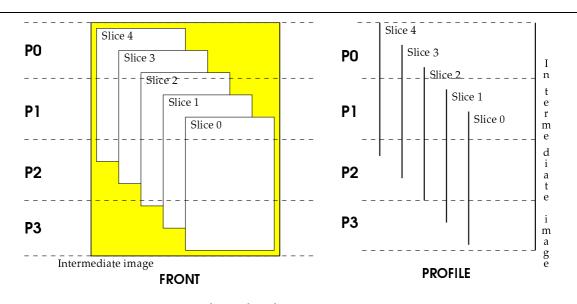

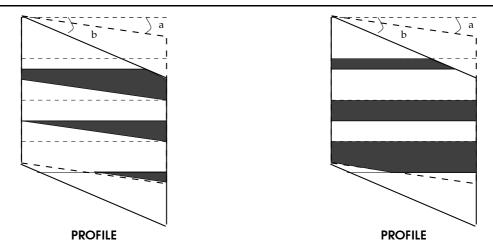

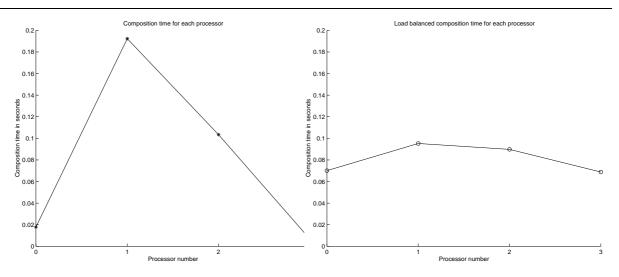

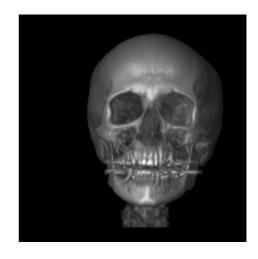

Cet article présente mes travaux avec F. Chaussumier sur l'équilibrage des charges et les recouvrements calculs/communications dans un algorithme de rendu volumique. C'est une extension à un problème irrégulier de mes travaux précédents qui concernaient le traitement de structures de données régulières.

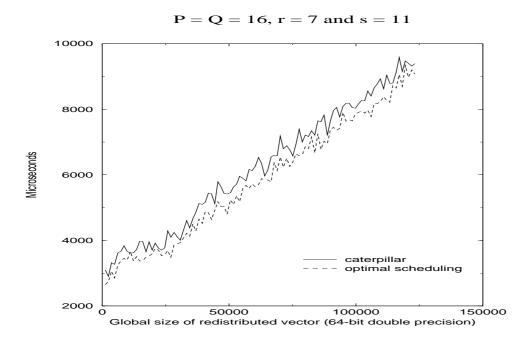

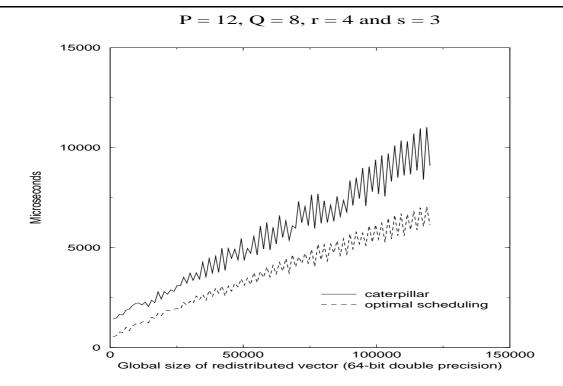

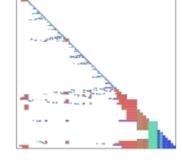

#### Chapitre E Scheduling Block-Cyclic Array Redistribution

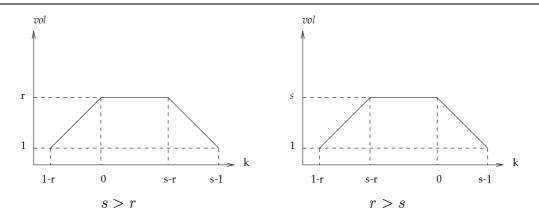

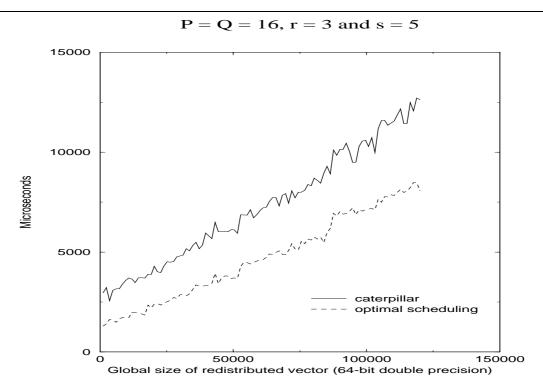

Ces travaux concerne l'optimisation de l'ordonnancement des communications pour le problème de la redistribution de données distribuées de manière cyclique par blocs sur un réseau de processeurs. Les applications de ce type de redistribution sont nombreuses (bibliothèques numériques parallèles, compilation d'HPF, etc.).

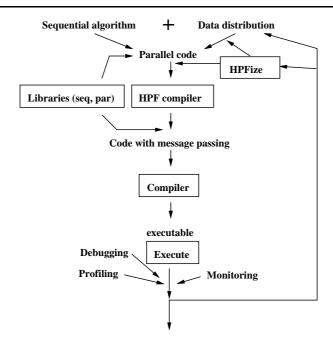

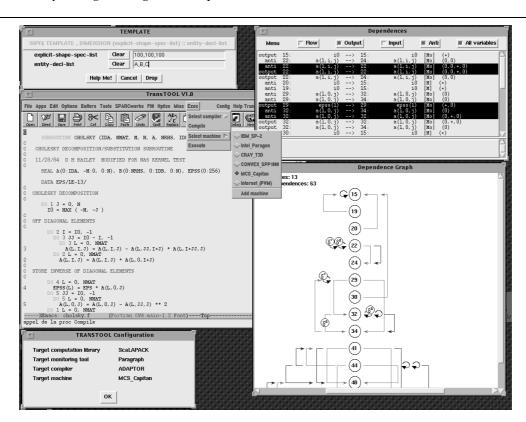

## Chapitre F HPFIT: A Set of Integrated Tools for the Parallelization of Applications Using High Performance Fortran

Cet article présente une partie du projet HPFIT avec notamment les travaux autour de la parallélisation automatique et la recherche de schémas macro-pipelines.

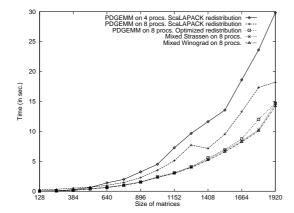

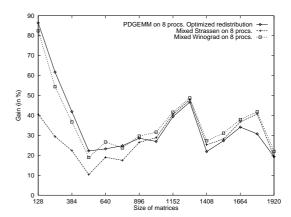

## Chapitre G Mixed Parallel Implementations of the Top Level Steps of Strassen and Winograd Matrix Multiplication Algorithms (2001)

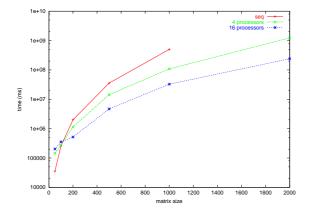

Ces travaux présentent mes derniers travaux autour de l'algorithmique parallèle mixte, c'est-à-dire qui utilise à la fois le parallélisme de données et le parallélisme de tâches. Nous avons optimisé les

communications et le placement de données pour deux algorithmes classiques de l'algèbre linéaire, Strassen et Winograd.

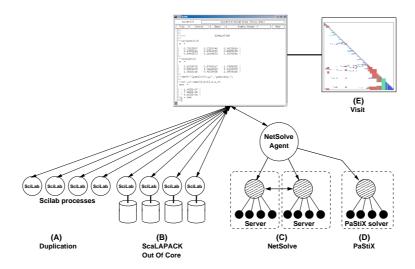

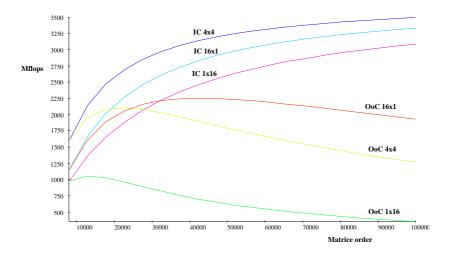

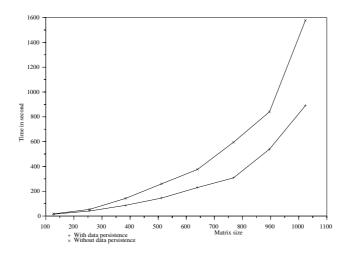

#### Chapitre H Scilab to Scilab// - The OURAGAN Project (2001)

Cet article représente un bilan du projet OURAGAN dont le but est de paralléliser l'outil SCILAB avec différentes approches (bibliothèques de communication, interfaces pour des bibliothèques d'algèbre linéaire parallèle, serveurs de calcul).

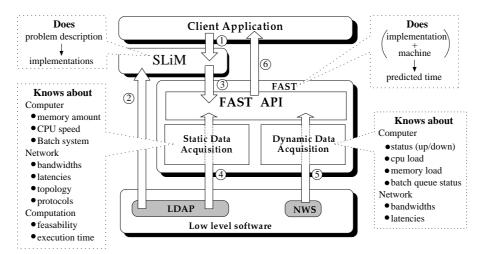

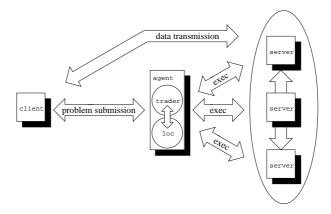

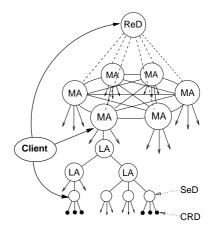

#### Chapitre I A Scalable Approach to Network Enabled Servers (2001)

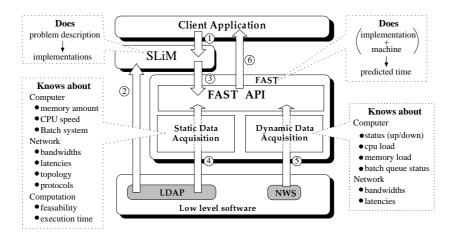

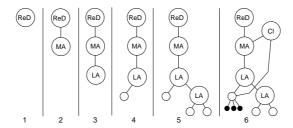

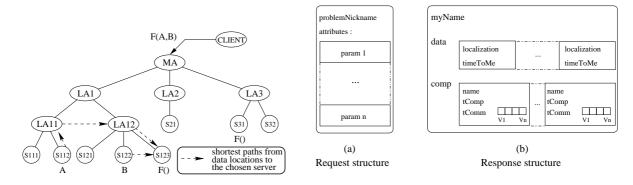

Cet article présente mes travaux les plus récents sur le développement d'un environnement extensible pour la mise en place d'applications de type ASP (Application Service Provider) dans un environnement de metacomputing.

## CONTRIBUTION TO PARALLEL ALGORITHMIC

#### Numerical Computation: from Libraries to Metacomputing Environments

Appendix: vita and publications

#### Frédéric Desprez

July 20th, 2001

This document presents some of my main publications since my PhD defense.

#### Chapter A Vita (french)

I describe my research, teaching and administrative work since my PhD and it gives a list of all my publications.

#### Chapter B Optimization of a LU Factorization Routine Using Communication/Computation Overlap

This first paper presents my work in collaboration with S. Domas and B. Tourancheau around the optimization of the LU factorization using overlap of computation by communication. Even if the gains obtained are not that important (maximum of 20%), we managed to give an accurate model of this optimization that leads to a general model of this routine. Then the results were used in ALASCA to compute the computation cost of some numerical routines to be able to guess the most efficient distributions.

#### Chapter C Optimal Grain Size Computation for Pipelined Algorithms (1996)

This work started during my year at LaBRI in collaboration with P. Ramet and J. Roman. The results presented in this paper extend the results presented in my PhD thesis to general complexity functions for computations and communications. A library was developed that gives the optimal packet size to the LOCCS library routines.

## Chapter D Communications Optimizations and Efficient Load-balancing for a Volume Rendering Algorithm on a Cluster of PCs (2000)

This paper presents my work in collaboration with F. Chaussumier around the load-balancing and the overlap of communications in a volume rendering application. This is an extension of my previous work to irregular computations.

#### Chapter E Scheduling Block-Cyclic Array Redistribution

This paper describes the optimization of the scheduling of communications for the problem of the redistribution of a matrix distributed in a block-cyclic way on a network of processors. There are many applications of such redistribution (parallel numerical libraries, HPF compilation, ...).

## Chapter F HPFIT: A Set of Integrated Tools for the Parallelization of Applications Using High Performance Fortran

This paper presents a part of the HPFIT project and more precisely our work around automatic parallelization and the generation of macro-pipeline communications.

## Chapter G Mixed Parallel Implementations of the Top Level Steps of Strassen and Winograd Matrix Multiplication Algorithms (2001)

This papers describes my latest work around mixed-parallelism, i.e. the simultaneous use of data and task parallelism. We optimized the communications and data distribution for two basic linear algebra algorithms, Strassen and Winograd.

#### Chapter H Scilab to Scilab $_{//}\,$ – The OURAGAN Project (2001)

This paper presents the OURAGAN project whose goal is to parallelize the SCILAB tool using different approaches (message-passing libraries, interfaces for parallel numerical libraries, computational servers).

#### Chapter I A Scalable Approach to Network Enabled Servers (2001)

This papers describes my latest work around the development of a scalable environment for ASP (Application Service Provider) applications in a grid environment.

## Table des matières

| Α | Cur  | rriculum vitae                                                                       | 3        |

|---|------|--------------------------------------------------------------------------------------|----------|

|   | A.1  |                                                                                      | 4        |

|   |      | Développement de logiciels                                                           | 5        |

|   | A.3  | Encadrement de jeunes chercheurs                                                     | 6        |

|   |      | Activités d'évaluation                                                               | 8        |

|   | A.5  | Participation à des projets de recherche avec l'industrie                            | 9        |

|   | A.6  | Collaboration nationales et internationales                                          | 10       |

|   | A.7  | Tâches collectives                                                                   | 12<br>14 |

|   | A.8  | Publications                                                                         | 14       |

|   | A.3  | Tublications                                                                         | 10       |

| В | Opt  | timization of a LU Factorization Routine                                             | 21       |

|   | B.1  | Introduction                                                                         | 22       |

|   | B.2  | Parallel Block $LU$ Decomposition                                                    | 22       |

|   | B.3  |                                                                                      | 24       |

|   | B.4  | Analysis and Optimization of the ScaLAPACK LU Factorization                          | 25       |

|   | B.5  | Conclusion and future work                                                           | 34       |

|   | B.6  | References                                                                           | 35       |

| С | Opt  | timal Grain Size Computation for Pipelined Algorithms                                | 37       |

|   | -    |                                                                                      | 38       |

|   | C.2  |                                                                                      | 39       |

|   | C.3  | Experiments                                                                          | 42       |

|   |      | Conclusion and future works                                                          | 43       |

|   | C.5  | References                                                                           | 44       |

| D | Coi  | mmunications Optimizations and Efficient Load-balancing for a Volume Rendering Algo- |          |

|   | rith |                                                                                      | 45       |

|   | D.1  | Introduction and motivations                                                         | 46       |

|   | D.2  |                                                                                      | 46       |

|   | D.3  | Parallel algorithm                                                                   | 47       |

|   | D.4  | Optimizations                                                                        | 50       |

|   | D.5  | Experimental results                                                                 | 51       |

|   |      | Conclusion                                                                           | 54       |

|   | D.7  | References                                                                           | 55       |

| Ε | Sch  | neduling Block-Cyclic Array Redistribution                                           | 57       |

|   |      | Introduction                                                                         | 58       |

|   | E.2  | Motivating Examples                                                                  | 59       |

|   | E.3  | Literature overview                                                                  | 63       |

|   | E.4  | Main Results                                                                         | 65       |

|   | E.5  | MPI Experiments                                                                      | 75       |

|   | E.6  | Conclusion                                                                           | 77       |

|   | F 7  | References                                                                           | 78       |

TABLE DES MATIÈRES 1

| F | HPI | FIT : A Set of Integrated Tools for the Parallelization of Applications Using HPF | 81  |

|---|-----|-----------------------------------------------------------------------------------|-----|

|   | F.1 | Introduction                                                                      | 82  |

|   | F.2 | Previous Work                                                                     | 82  |

|   | F.3 | The HPFIT Project                                                                 | 83  |

|   | F.4 | TransTOOL                                                                         | 85  |

|   | F.5 | Optimization Kernel                                                               | 87  |

|   | F.6 | Conclusion and Future Work                                                        | 91  |

|   | F.7 | References                                                                        | 92  |

| G | Mix | ed Parallel Implementations of Strassen and Winograd Algorithms                   | 95  |

|   | G.1 | Introduction                                                                      | 96  |

|   | G.2 | Strassen and Winograd algorithms                                                  |     |

|   | G.3 | Mixed parallel algorithms                                                         |     |

|   | G.4 | Time cost models                                                                  |     |

|   | G.5 | Experimental results                                                              |     |

|   | G.6 | Conclusion and future work                                                        |     |

|   |     | References                                                                        |     |

| Н | Sci | lab to Scilab <sub>//</sub> - The OURAGAN Project                                 | 107 |

|   |     | Introduction                                                                      | 108 |

|   |     | SCILAB Processes Duplication                                                      |     |

|   |     | Network-Enabled Servers                                                           |     |

|   |     | Conclusion and future work                                                        |     |

|   |     | References                                                                        |     |

| ı | A S | calable Approach to Network Enabled Servers                                       | 125 |

|   | I.1 | Introduction                                                                      | 126 |

|   | I.2 | DIET architecture and related tools                                               | 126 |

|   | I.3 | CORBA based communication layer                                                   |     |

|   | I.4 | DIET initialization and operation                                                 |     |

|   | I.5 | Conclusion and future work                                                        |     |

|   | I.6 | References                                                                        |     |

Ce document suit les indications pour la constitution du dossier de candidature à l'inscription à l'Habilitation à Diriger des Recherches de l'Université Claude Bernard – Lyon I, précisées par la DAED (document jaune). Les éléments suivants y sont développés :

- mon Curriculum-Vitae (section A.1),

- mes développements logiciels (section A.2),

- mes travaux d'encadrement de jeunes chercheurs (section A.3),

- mes activités d'évaluation (section A.4),

- mes participations à des projets de recherche avec l'industrie (section A.5),

- mes collaborations nationales et internationales (section A.6),

- mes tâches collectives (section A.7),

- mes activités en enseignement (section A.8).

- la liste de mes publications (section A.9).

#### A.1 Curriculum-Vitae

#### Frédéric DESPREZ

## CR1 - INRIA Rhône-Alpes Responsable scientifique du projet CNRS-ENS Lyon-INRIA ReMaP

Né le 2 novembre 1964 à Beauvais (Oise)

Marié, 3 enfants

Dégagé des obligations militaires

Nationalité: française

| Adresse personnelle : | Adresses professionnelles :                                                  |                               |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------|-------------------------------|--|--|--|--|

|                       | Laboratoire de l'Informatique du Parallélisme                                | INRIA Rhône-Alpes             |  |  |  |  |

|                       | Ecole Normale Supérieure de Lyon                                             | ZIRST, 655 avenue de l'Europe |  |  |  |  |

| 40 rue du Stade       | 46 Allée d'Italie                                                            | Montbonnot                    |  |  |  |  |

| 38550 SABLONS         | 69364 Lyon Cedex 07                                                          | 38334 Saint Ismier Cedex      |  |  |  |  |

| Tel: 04 74 84 24 53   | Tel: 04 72 72 85 69                                                          | Tel : 04 76 61 53 48          |  |  |  |  |

| Mob: 06 12 92 60 03   | Fax: 04 72 72 80 80                                                          | Fax: 04 76 61 52 52           |  |  |  |  |

|                       | E-mail : Frederic.Desprez@inria.fr<br>URL : http://www.ens-lyon.fr/~desprez/ |                               |  |  |  |  |

#### Responsabilité au sein de l'INRIA

2000- Responsable scientifique du projet ReMaP.

**1997-** Suivi des thèses passées dans l'Unité de Recherche Rhône-Alpes.

#### **Formation**

**1994** (6 Janvier) Thèse de Doctorat INP Grenoble, LIP (Laboratoire de l'Informatique du Parallélisme) : "Procédures de base pour le calcul scientifique sur machines parallèles à mémoire distribuée" sous la direction de B. Tourancheau (C.R. CNRS) et la responsabilité administrative de M. Cosnard (Prof. ENS Lyon). Jury : Denis Trystram (Président), Gaétan Libert et Yves Robert (rapporteurs), Gérard Authié, Michel Cosnard et Bernard Tourancheau (examinateurs) et Jack Dongarra et Marc Garbey (invités).

**1990** D.E.A. d'Informatique fondamentale (ENS Lyon - 06/90) "Algèbre Linéaire sur Tnode" DEA préparé au Laboratoire LIP de l'ENS Lyon sous la direction de B. Tourancheau.

**1989** Maîtrise d'informatique (Grenoble - 06/89 - Mention AB).

**1987** Licence d'informatique (Grenoble - 06/87 - Mention AB).

#### Séjours à l'étranger de plus de 3 semaines

| 1996 | 1 mois dans le Computer Science Dept. à l'Université du Tennessee (Knoxville - USA) dirigé |

|------|--------------------------------------------------------------------------------------------|

|      | par le Professeur Dongarra.                                                                |

| 1994 | 8 mois de postdoc dans le Computer Science Dept. de l'Université du Tennessee.             |

| 1993 | 1 mois dans le Computer Science Dept. à l'Université du Tennessee.                         |

#### Stages, emplois et service militaire

| 1998-<br>1995-98 | CR 1 INRIA Rhône-Alpes, projet ReMaP.<br>CR 2 INRIA Rhône-Alpes, projet ReMaP.                                                                                          |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1994-95          | Maître de Conférences à l'ENSERB (Université Bordeaux I) et recherche au LaBRI (équipe ALIENOR dirigée par Jean Roman).                                                 |

| 1990-93          | Thèse de doctorat au LIP.                                                                                                                                               |

| 1990             | Chef de projet chez SMART (Valence) pendant 6 mois. Protection d'un réseau Unix du CNET (Issy-les-Mlx) avec des cartes à puces. Conduite de l'ensemble du projet (de la |

|                  | spécification à la réalisation) et encadrement d'un ingénieur.                                                                                                          |

| 1990             | Stage de DEA au LIP (4 mois). Etude d'algorithmes parallèles fondamentaux et implémentation sur Tnode (TELMAT) à base de Transputers.                                   |

| 1989             | Stage de 2 mois au LIP. Etude et réalisation d'algorithmes de produit de matrices parallèles sur machine Tnode.                                                         |

| 1988             | Service militaire au 27° RCS de Grenoble (création d'une base de données sur un PC et formation des appelés et des secrétaires).                                        |

#### Langues étrangères

Anglais parlé, lu et écrit couramment.

#### Participations à des projets nationaux, industriels et internationaux

Entre parenthèse la période pendant laquelle j'ai travaillé sur un projet.

#### • Eureka EuroTOPS (6/93-10/98)

Responsable scientifique (95-97)

Responsable tâche bibliothèques de calcul parallèles (09/93-12/95)

Responsable tâche outil de parallélisation de codes Fortran 77 (10/95-10/98)

#### • **INCO-DC Paralin** (06/96-09/99)

Responsable tâche parallélisation logiciel Scilab (06/96-06/98)

#### • TTN ProHPC (03/97-09/99)

Responsable action ACRA/Solid Dynamics (03/97-02/98)

Responsable action ACRA/CADOE (03/97-02/98)

Responsable action DYNA (03/98-10/98)

Responsable action METAL (09/98-01/99)

#### • ARC INRIA OURAGAN (01/98-12/00)

Responsable de l'ARC (90-00)

#### • RNRT VTHD (01/99-12/01)

Responsable du sous-projet 5 pour l'UR Rhône-Alpes Responsable de l'action Scilab//

#### A.2 Développement de logiciels

Mes travaux ont donné lieu à des développements logiciels importants. Certains de ces développements ont été réalisés dans le cadre des projets Eureka EuroTOPS, TTN ProHPC, PARALIN et l'ARC INRIA OU-RAGAN (décrits dans la section A.5).

TransTool Intégration des différents outils dans un seul environnement, développement des interfaces C, Lisp et TCL, développement du noyau d'optimisation, d'HPFize (outil d'insertion de directives), etc. (en collaboration avec A. Darte, J.-C. Mignot, C. Randriamaro, G. Silber).

- Scalapack Optimisation de la factorisation LU de Scalapack et développement d'une routine de calcul de taille de bloc optimale (fonction de la taille de la matrice et du nombre de processeurs), étude de la redistribution de matrices (en collaboration avec J. Dongarra, S. Domas, A. Petitet, C. Randriamaro et Y. Robert). Scalapack est diffusé par ftp.

- LOCCS Développement d'une version améliorée des LOCCS (avec interface portable MPI¹ avec nouvelles routines (en collaboration avec P. Ramet et F. Chaussumier).

- Adaptor Amélioration de l'intégration des LOCCS dans Adaptor, amélioration du driver, nouveaux types de schémas traités, etc. (en collaboration avec T. Brandes et J. Zory). Adaptor est diffusé par ftp.

- Scilab Intégration de PVM comme couche de communication d'une version parallèle de Scilab, développement d'une interface ScaLAPACK et définition des serveurs de calcul (en collaboration avec les membres de l'ARC INRIA OURAGAN). Scilab est un logiciel diffusé mondialement par ftp, notamment grâce à sa version Linux.

#### A.3 Encadrement de jeunes chercheurs

Je soutiendrais mon Habilitation à Diriger des Recherches début Juin 2001.

#### A.3.1 Etudiants en thèse

#### A.3.1.1 Thèse de Stéphane Domas

J'ai co-encadré à 75 %S. Domas (MENRT au LIP) avec Bernard Tourancheau sur des problèmes d'algèbre linéaire en parallèle. Son but était d'améliorer une bibliothèque existante (ScaLAPACK) en proposant de nouveaux algorithmes plus adaptés à une parallélisation, soit en proposant des nouveaux schémas de distribution de données ou en utilisant des pipelines de calculs et de communications.

Stéphane Domas a soutenu sa thèse le 23 Octobre 98. Il a été recruté en 2000 après son service militaire et un an d'ATER comme Maître de Conférences à l'IUT de Belfort et effectue sa recherche au LIFC dans l'équipe de Jean-Marc Nicod.

#### A.3.1.2 Thèse de Pierre Ramet

J'ai co-encadré P. Ramet avec Jean Roman (LaBRI) (25/75) sur des problèmes de recouvrements calculs/communications dans les codes scientifiques. Son but était de développer des techniques de calcul de grain pour des algorithmes pipelines lorsque les polynômes caractérisant les calculs (ou les communications) ne sont pas forcément des fonctions linéaires de la taille des données. Il a travaillé également sur un solveur parallèle creux de type Cholesky Crout.

Pierre Ramet a soutenu sa thèse le 12 Janvier 2000 et il a été recruté comme Maître de Conférences à l'IUT de Bordeaux I et effectue sa recherche au LaBRI dans l'équipe de Jean Roman.

#### A.3.1.3 Thèse de Cyrille Randriamaro

J'ai co-encadré Cyrille avec Yves Robert (50/50) sur des problèmes de distribution et redistribution semiautomatiques de matrices avec HPF dans le cadre du projet TransTool. Il a également travaillé sur l'optimisation de l'ordonnancement des communications pour la redistribution de matrices distribuées avec des schémas cycliques par blocs.

Cyril a soutenu sa thèse le 24 Janvier 2000 et a été recruté comme Maître de Conférence à l'Université d'Amiens et effectue sa recherche au LaRIA dans l'équipe de J.-F. Myoupo.

<sup>&</sup>lt;sup>1</sup>Message Passing Interface

#### A.3.1.4 Thèse de Frédérique Chaussumier (soutenance en Juin 2001)

Frédérique (3ème année de CIFRE avec MS&I², 50% avec M. Loi) a travaillé sur l'optimisation des communications dans des applications irrégulières et sur environnement hétérogène. Dans un premier temps, elle a travaillé sur l'optimisation d'un algorithme de rendu volumique 3D en utilisant des techniques de recouvrement calcul/communication et d'équilibrage des charges élastique. La machine cible était une grappe de PC connectés par un réseau Myrinet et les contraintes industrielles étaient d'obtenir un rendu en temps réel lorsque l'on effectuait une rotation arbitraire du volume. Ensuite, elle a travaillé sur une application benchmark du programme américain ASCI, le Sweep3D en utilisant encore des techniques de pipelines.

#### A.3.1.5 Thèse de Frédéric Suter (en cours)

Frédéric (2ème année de MENRT au LIP, 100%) travaille sur des problèmes d'optimisation de codes numériques utilisant à la fois le parallélisme de tâches et le parallélisme de données. Les résultats de ses travaux seront utilisés par l'environnement DIET pour répartir la charge entre les divers serveurs.

#### A.3.1.6 Thèse de Martin Quinson (en cours)

Martin (1ère année de MENRT au LIP, 100%) travaille sur la mise en place de serveurs de calcul dans un environnement de metacomputing. Ses premiers travaux consistent à développer un outil d'évaluation de performances statiques et dynamiques de réseaux et de bibliothèques de calcul. Cet outil permettra à l'ordonnanceur d'un environnement de type Network Enabled Servers d'évaluer le coût des migrations de données entre serveurs et le coût de calcul des problèmes à résoudre sur ces mêmes serveurs.

#### A.3.2 Autres étudiants

#### Etudiants de DEA

- Martin Quinson, a effectué son DEA en 2000 à l'ENS. Martin a travaillé sur l'étude d'un environnement d'évaluation de performances dans un environnement de metacomputing et son intégration dans Scilab// (co-encadrement 50/50 avec F. Suter).

- Nathalie Viollet, a effectué son DEA en 2000 à l'ENS. Nathalie a étudié la mise en place d'une base LDAP pour la recherche de ressources logicielles dans un environnement de metacomputing et son intégration dans Scilab// (co-encadrement 25/75 avec J.-F. Méhaut).

- Laurent Bobelin, a effectué son DEA en 99 à l'ENS. Laurent a travaillé sur des heuristiques de placement de données pour des algorithmes à parallélisme mixte (co-encadrement 50/50 avec C. Randriamaro).

- Jacques-Alexandre Gerber, a effectué son DEA en 98 à l'ENS. Jacques-Alexandre a travaillé sur des outils de transformation automatique de programmes Fortran 77 contenant des appels de bibliothèques BLAS et LAPACK vers HPF (encadrement à 100%).

- **Fabrice Rastello**, a effectué son DEA en 97 à l'ENS. J'ai co-encadré Fabrice avec Yves Robert sur des optimisations de communications et du grain de calcul dans les codes numériques (technique du tiling) (co-encadrement 50/50 avec Y. Robert).

- Julien Zory, a effectué son DEA en 96 à l'ENS. Julien a étudié la recherche automatique de schémas macro-pipelines et a continué l'intégration de la bibliothèque LOCCS dans le compilateur HPF Adaptor (encadrement à 100%).

- Pierre Ramet, a effectué son DEA en 1995 au LaBRI. Pierre a travaillé sur des méthodes de calcul de taille de paquets optimales pour les pipelines de communication (co-encadrement 50/50 avec J. Roman).

- Pierre Garnier, a effectué son DEA en 1995 au LaBRI. Pierre a travaillé sur la parallélisation d'un code du CEA à l'aide de High Performance Fortran (co-encadrement 50/50 avec J. Roman).

- **Bruno Jargot**, a effectué son DEA en 1993 à l'ENS. Bruno a travaillé sur une interface orientée objet pour la bibliothèque LOCCS (encadrement à 100%).

<sup>&</sup>lt;sup>2</sup>Matra Système & Information

#### - Etudiants de DESS

Gilles Lebourgeois, du DESS de Strasbourg (option parallélisme). Gilles a travaillé sur l'analyse syntaxique et sur l'algorithme d'Allen et Kennedy dans le cadre du projet TransTool. A la suite du stage, Gilles a été recruté 2 ans comme ingénieur d'étude INRIA dans le cadre du projet TTN ProHPC.

- Lionel Tricon du DESS de Strasbourg (option parallélisme). Lionel a travaillé sur l'analyse de dépendances et sur la recherche de boucles *Cross-Processors* dans le cadre du projet TransTool. A la suite du stage, Lionel a été recruté 1 an comme ingénieur d'étude INRIA dans le projet ReMaP.

- **Frédéric Naquin**, du DESS de Lyon 1 (prom. 97) (option réseaux). Frédéric a comparé les différentes couches de communications sur les réseaux de type Myrinet.

#### - Etudiants de Maîtrise

- Stéphane Vernat, a effectué sa Maîtrise à Lyon 1 en 97. J'ai co-encadré S. Vernat avec Stéphane Ubéda sur la parallélisation du logiciel GRASS de systèmes d'information géographiques.

- Dominique Ponsard, a travaillé en 98 sur le portage d'une application de modèle numérique de terrain sous MPI. Il s'agit d'une collaboration avec G. Vidal du laboratoire des Sciences de la Terre de l'ENS Lyon. A la suite du stage, Dominique a été recruté comme ingénieur d'étude au CNRS.

- Martin Quinson, a effectué sa Maîtrise à St Etienne en 99. J'ai encadré M. Quinson sur l'optimisation de la routine de distribution et de récupération de données de la bibliothèque ScaLAPACK.

- Thierry Murgue, a effectué sa Maîtrise à St Etienne en 99. J'ai co-encadré T. Murgue avec S. Ubéda sur le développement d'une interface graphique de visualisation de matrices creuses distribuées dans Scilab.

#### - Autres encadrements

- Olivier Reymann, a travaillé en 96 sur la première version de TransTool, notamment sur l'étude de l'intégration de l'éditeur XEmacs dans une fenêtre Tk.

- **Nicolas Bert**, a travaillé en 96 sur le nettoyage de la bibliothèque LOCCS et sur sa version MPI.

#### A.4 Activités d'évaluation

#### A.4.1 Jurys (thèses, diplôme d'ingénieur)

J'ai été membre de plusieurs jurys de thèses

- **Asier Ugarte**, soutenue le 04 janvier 2001 à Bordeaux (rapporteur),

- Eddy Caron, soutenue le 14 décembre 2000 à Amiens (examinateur),

- **Fabrice Rastello**, soutenue le 6 septembre 00 à Lyon (examinateur),

- **Cyril Randriamaro**, soutenue le 24 janvier 00 à Lyon (directeur),

- Pierre Ramet, soutenue le 12 janvier 00 à Bordeaux (directeur),

- **Julien Zory**, soutenue le 17 décembre 99 à Paris (examinateur),

- **Stéphane Domas**, soutenue le 23 octobre 98 à Lyon (directeur),

- **David Laimani**, soutenue le 6 janvier 97 à Besançon (examinateur),

- **Makan Pourzandi**, soutenue le 20 janvier 95 à Lyon (examinateur).

et d'un jury de diplôme d'ingénieur CNAM :

- **Véronique Chabanis**, soutenu le 31 janvier 00 à Grenoble (examinateur).

#### A.4.2 Autres tâches d'évaluation

J'ai du évaluer en 1997 le dossier déposé à la région Aquitaine par Serge Chaumette (LaBRI, Université de Bordeaux).

Cette année, j'ai dû évaluer une proposition de BQR pour l'INSA de Lyon ainsi qu'un projet autour de l'utilisation d'une plate-forme de type grille de calcul pour le gouvernement belge.

#### A.5 Participation à des projets de recherche avec l'industrie

#### A.5.1 Projet Eureka EuroTOPS

Le projet Eureka EuroTOPS avait pour but le développement d'outils pour la parallélisation d'applications sur machines parallèles à mémoire distribuée. C'était un projet européen dont les partenaires étaient Matra Systèmes et Information (MS&I), l'ENS Lyon, l'INRIA, le CNRS, Simulog, ESI, NA Software, et quelques autres. Les machines cibles étaient la CAPITAN et le cluster de PC avec réseau Myrinet Peak-Server installées au LIP.

Dans ce projet, j'ai participé dans un premier temps à la tâche portant sur les bibliothèques de calcul numérique parallèles et leur portage sur la machine CAPITAN. Mes travaux sur l'algèbre linéaire parallèle cités précédemment entrent directement dans ce projet.

Ma seconde tâche dans EuroTOPS consistait dans le développement du logiciel TransTool et de son utilisation avec les outils de Simulog et NaSoftware.

De 1996 à la fin du projet (décembre 98), j'ai été en outre le responsable scientifique du projet pour le LIP.

#### A.5.2 Projet INCO-DC Paralin

J'ai participé à la mise en place du projet PARALIN. Ce projet était un projet INCO-DC de la communauté européenne avec des partenaires universitaires et industriels de France, du Chili, d'Espagne et d'Uruguay. Le but était le transfert industriel du calcul parallèle dans l'industrie minière et de l'énergie au Chili et en Uruguay. Ce projet est en relation avec le projet PARANDES<sup>3</sup> dont le but était l'installation d'une machine CAPITAN au Chili.

L'INRIA était impliquée dans ce projet avec les projets ReMaP et Promath (INRIA Rocquencourt). Notre travail a consisté à porter une application d'optimisation de réseau électrique sur la version parallèle de Scilab à l'aide de PVM en collaboration avec Frédéric Bonnans de Promath.

Le projet s'est terminé en septembre 1999.

#### A.5.3 Projet TTN-ProHPC

J'ai participé pour le LIP et ReMaP à l'écriture du projet HPCN TTN ProHPC dont le but était de promouvoir l'utilisation du calcul parallèle dans l'industrie [BBD+98]. Le projet était constitué de quatre partenaires : l'ENS Lyon (coordinateur), l'INRIA, MS&I et Simulog.

J'étais responsable pour le LIP de deux tâches du TTN dans l'action ACRA pour la dissémination du calcul à haute performances dans les PME de la région. Les deux sociétés, CADOE et Solid Dynamics, ont développé des logiciels dans le domaine de la mécanique (simulation). J'ai participé à la parallélisation de ces logiciels en collaboration avec les ingénieurs du TTN en poste au LIP, C. Barberet et G. Lebourgeois.

L'action ACRA avec CADOE a donné lieu à une suite : le projet DYNA. Dans ce projet, j'ai étudié avec G. Lebourgeois la parallélisation du noyau de calcul du logiciel, en l'occurence un solveur creux itératif.

Un autre projet du même type a démarré avec la société SYSTUS : le projet METAL avec un code d'éléments finis. J'ai étudié la parallélisation du logiciel de la société en collaboration avec un ingénieur de recherche INRIA, R. Choquet.

Le projet s'est terminé en septembre 1999.

#### A.5.4 Projet RNRT VTHD

Le but du projet RNRT VTHD <sup>4</sup> est de connecter une certains nombre de centres de recherche de France Telecom et toutes les Unités de Recherche INRIA par un réseau à très haut débit (2.5 Gigabits par seconde). De nombreuses recherches sont effectuées autour des aspects réseaux et un sous-projet concerne les applications qui permettront d'exhiber les limites d'un tel réseau et les problèmes dus à sa mise en place. Je suis

<sup>&</sup>lt;sup>3</sup>du programme ITDC'94.

<sup>&</sup>lt;sup>4</sup>réseau à Vraiment Très Haut Débit.

responsable de ce sous-projet au niveau de l'UR Rhône–Alpes et je l'anime au niveau national avec Thierry Priol.

Nous avons également proposé une action de ce sous-projet dont le but est de porter nos serveurs de calcul sur le réseau VTHD. Une telle bande-passante va nous permettre de déporter des calculs avec un grain plus fin. Nous recrutons actuellement un postdoctorant (Eddy Caron) sur le sujet.

Le projet se terminera en décembre 2001.

#### A.5.5 Proposition de projet RNTL GASP

Je suis le responsable du projet RNTL GASP (Grid Application Service Provider) qui vient d'être déposé au ministère de l'industrie en février. Ce projet a pour but de développer une infrastructure logicielle permettant la mise en place simple et performante d'applications de type ASP sur une plate-forme de metacomputing. Les partenaires sont le projet ReMaP, le projet Résédas de l'INRIA Lorraine, l'équipe SDRP du LIFC, le laboratoire IRCOM, le laboratoire des Sciences de la terre de l'ENS Lyon et Sun Labs.

#### A.6 Collaboration nationales et internationales

#### A.6.1 Relations académiques

#### A.6.1.1 Computer Science Dept, The University of Tennessee, Knoxville, USA

J'ai collaboré avec l'équipe du Professeur Dongarra, autour de ScaLAPACK et en particulier de la redistribution de matrices dans le cadre d'un PICS, d'un projet CNRS-NSF puis d'un projet INRIA-NSF. Nous sommes en train de mettre en place une nouvelle collaboration avec l'équipe de Jack Dongarra autour du logiciel NetSolve et avec l'équipe de Rich Wolsky autour du logiciel NWS.

Par ailleurs, j'ai effectué un postdoctorat de huit mois dans ce même laboratoire à partir de février 1994. En accord avec Jack Dongarra, j'ai continué mes recherches sur les bibliothèques de calcul et de communication en les intégrant dans les outils développés dans son laboratoire. J'ai pu ainsi valider certaines méthodes sur différentes nouvelles machines et aider les chercheurs à obtenir des codes performants et lisibles grâce à mes bibliothèques. J'ai également travaillé sur les routines de distribution et de récupération de données dans ScaLAPACK.

J'ai ensuite effectué un séjour de trois semaines durant lequel nous avons travaillé sur la redistribution de données [DDP+98].

#### A.6.1.2 GMD/SCAI, Bonn, Allemagne

J'ai collaboré pendant trois ans avec T. Brandes. Thomas est le concepteur du compilateur HPF Adaptor. Nous avons travaillé sur l'intégration de la bibliothèque LOCCS dans le compilateur et sur la définition des fonctionnalités de TransTool.

#### A.6.1.3 LaBRI, Bordeaux

Collaborations avec J. Roman, S. Chaumette, M.-C. Counilh, F. Pellegrini et P. Ramet de l'équipe ALIE-NOR dans le cadre du projet HPFIT autour de la visualisation de données distribuées et de la parallélisation d'applications manipulant des structures de données creuses, sur les bibliothèques LOCCS et OPIUM et dans le cadre de l'ARC INRIA OURAGAN autour de l'utilisation de solveurs creux parallèles dans Scilab.

#### A.6.1.4 Résédas, INRIA-LORIA, Nancy

Collaboration avec E. Fleury et E. Jeannot dans le cadre de l'ARC INRIA OURAGAN autour de l'optimisation du logiciel Netsolve (ajout de persistence de données sur les serveurs et ordonnancement des tâches) et interfacage de Scilab avec la bibliothèque ScaLAPACK.

#### A.6.1.5 LIFC, Université de Franche-Comté, Besançon

Collaboration avec J.-M. Nicod et son équipe dans le cadre de l'ARC INRIA OURAGAN autour de la gestion de serveurs sous CORBA et pour le développement d'un environnement hiérarchique d'agents.

#### A.6.1.6 LARIA, Université de Picardie, Amiens

Collaboration avec G. Utard et son équipe dans le cadre de l'ARC INRIA OURAGAN autour de l'interfacage de Scilab avec des bibliothèques out-of-core et l'ajout de types distribués dans Scilab.

#### A.6.1.7 Métalau, INRIA Rocquencourt

Collaboration avec C. Gomez, S. Steer et M. Goursat dans le cadre de l'ARC INRIA OURAGAN autour de la parallélisation de Scilab.

#### A.6.2 Autres relations académiques

**Projet Promath, INRIA Rocquencourt :** Collaboration avec F. Bonnans autour de la parallélisation d'algorithmes d'optimisation avec Scilab (projet PARALIN).

J'ai participé aux diverses actions nationales de collaborations inter-laboratoires comme CAPA, RU-MEUR, iHPERF et Grappes.

#### A.6.2.1 Projets académiques

**ARC INRIA OURAGAN** J'ai été responsable de l'ARC OURAGAN (Janvier 99–Décembre 2000) qui a fait collaborer trois projets (Métalau à Rocquencourt, Résédas à Nancy et ReMaP à Lyon) et trois équipes (ALIENOR au LaBRI, l'équipe de J.-M. Nicod au LIFC et l'équipe de G. Utard au LaRIA).

Les objectifs sont d'offrir aux utilisateurs l'accès à diverses ressources de calcul (qu'elles soient matérielles ou logicielles) et ce, même si ces dernières sont distribuées au sein un réseau. Le but est d'avoir une plate-forme performante, facile d'utilisation (i.e., pas réservée uniquement aux seuls experts en programmation parallèle) intégrant les mécanismes nécessaires pour pouvoir effectuer et utiliser des ressources de calcul de façon distante. La facilité d'utilisation est primordiale et l'aspect interactif que l'on retrouve dans Scilab doit être conservé. La performance est garantie par l'intégration de bibliothèques parallèles de calcul dense et creux au sein du logiciel Scilab et par la mise en œuvre de politiques de redistribution, de répartition de charge permettant d'utiliser au mieux les ressources de calcul disponibles et ce de la façon la plus transparent possible pour l'utilisateur qui peut continuer à développer et prototyper ses applications en ligne.

Nous avons obtenu un financement de l'INRIA qui nous a permis de recruter un postdoctorant pour un an (E. Jeannot). Le travail d'Emmanuel a consisté à étudier NetSolve et à le modifier pour mettre en place l'architecture logicielle de nos serveurs de calcul. Il a par ailleurs étudié l'interfacage de bibliothèques parallèles de calcul creux au sein d'un outil comme Scilab (définition de nouveaux types et de nouveaux opérateurs).

L'ARC OURAGAN s'est terminée en décembre 2000.

**Projet NSF–INRIA autour du creux** J'ai participé à la mise en place d'une proposition de contrat NSF–INRIA sur des préconditionnements robustes et parallèles. Côté français, je suis coordinateur avec B. Philippe de l'IRISA. Y. Saad de l'Université du Minnesota est le coordinateur côté américain. Les laboratoires impliqués sont en France le CERFACS, le projet ReMaP, le projet ALADIN, le LaBRI et aux Etats–Unis l'Université du Minnesota, l'Université de l'Indiana et le Lawrence Berkeley Lab. Le projet concerne le développement de procédures de résolution de très grands systèmes linéaires à l'aide de méthodes itératives, directes et hybrides. J'interviens pour l'optimisation l'algorithmes numériques parallèles.

Montage d'un projet NSF-INRIA autour de NetSolve Je suis en train de mettre en place un programme NSF-INRIA entre l'Université du Tennessee, le projet Résédas de l'INRIA Lorraine et le projet ReMaP autour de nos travaux sur NetSolve. Cette collaboration a démarrée suite à la visite de Martin Quinson et Emmanuel Jeannot dans le laboratoire de Jack Dongarra. Ayant optimisé le logiciel NetSolve de manière importante grâce à nos recherches autour de Scilab (amélioration des transferts de données, augmentation de la précision des prédictions des coûts de calcul et de communication dans la grille, etc.), les chercheurs travaillant sur NetSolve nous ont proposé de mettre en place cette collaboration et de la financer en partie grâce à un programme NSF-INRIA.

**Fédération de calcul lyonnaise** J'ai participé à la réponse à l'appel d'offre de la région Rhône–Alpes. Le but de cette action est la mise en place d'une fédération de laboratoires et donc de rassembler les forces de calculs des divers centres de calcul et laboratoires lyonnais afin de favoriser les échanges entre les chercheurs de diverses disciplines. Nous avons proposé d'apporter notre expertise en matière d'algorithmique parallèle et de metacomputing ainsi que le portage d'une application sur la plate-forme obtenue grâce au financement de la région.

#### A.6.3 Relations industrielles

#### A.6.3.1 Sun Labs, Meylan

Je suis en train de mettre en place une collaboration avec la société Sun Microsystems et son entité de recherche Sun Labs autour de serveurs de calculs accessibles depuis Internet. Nous avons proposé un projet RNTL (Grid Application Service Provider ou GASP) avec eux et d'autres partenaires académiques.

#### A.6.3.2 Autres relations industrielles

En plus de mes collaborations avec des sociétés privées lors de projets industriels (voir chapitre A.5), j'ai travaillé plus précisement avec la société Simulog pour interfacer nos développements autour de TransTool avec l'outil Forsys-Partita.

#### A.7 Tâches collectives

#### A.7.1 Direction du projet ReMaP

Depuis Septembre 2000, j'ai pris la suite d'Yves Robert à la direction du projet CNRS–INRIA–ENS Lyon ReMaP <sup>5</sup>. Ce projet regroupe 10 permanents et 10 doctorants.

#### A.7.2 Organisation de conférences

En 1994, j'ai organisé avec S. Ubéda les Journées Industrielles du Parallélisme (JIP) à l'ENS. Ces journées avaient pour but de présenter aux industriels l'utilisation du parallélisme grâce à une série de cours, de présentations de "success stories" d'autres industriels et d'une journée de travaux pratiques sur machines (réseau de stations de travail). Nous avions également invité des vendeurs de machines pour qu'ils présentent leurs produits. Notre but était également de rencontrer les industriels et d'essayer d'évaluer leurs problèmes de performances afin d'orienter certaines de nos recherches pour leur résolution. En 1995, j'ai organisé la deuxième série de journées sur le même thème avec Jean Roman à l'ENSERB à Bordeaux.

J'ai participé avec Jack Dongarra à la mise en place de la série de conférences "European PVM Users Group Meeting" (appelée maintenant EuroPVM–MPI) dont la première édition a eu lieu en 1994 à Rome.

J'ai fait partie du comité d'organisation de RenPar'96, Rencontres Francophones du GDR PRS, qui ont eu lieu à Bordeaux en mai 96. J'étais entre autre responsable d'une journée applications parallèles.

<sup>&</sup>lt;sup>5</sup>http://www.ens-lyon.fr/~desprez/ReMaP/

A.7 Tâches collectives

Je suis co-organisateur avec Jean-François Méhaut, Yves Robert et Eric Fleury du Workshop MSA <sup>6</sup> (*Metacomputing Systems and Applications*) qui a eu lieu en 2000 à Toronto en marge de la conférence ICPP'2000 (*International Conference on Parallel Processing*) et qui aura lieu cette année à Valence (Espagne) en septembre (durant ICPP'2001). L'objectif de ce workshop est de confronter les recherches sur les environnements exécutifs et les applications pour le metacomputing.

#### A.7.3 Comités d'édition

J'ai été co-éditeur (avec B. Tourancheau et L. Prylli) d'un numéro spécial de la revue Calculateurs Parallèles sur PVM (volume 8, numéro 2, date 1996).

#### A.7.4 Comités de programmes

J'ai fait partie du comité de programme d'EuroPar'96 et j'étais local-chair de la session *High-Performance Computing and Applications* qui a eu lieu à Lyon en août 1996. J'ai fait partie du comité de programme de la Conférence EuroPVM'96 qui a eu lieu début octobre à Munich. J'ai fait partie du comité de programme d'EuroPar'97 et j'étais co-chair de la session "Applications Industrielles". J'ai été invité à être local-chair de la conférence EuroPAR'99 qui a eu lieu à Toulouse en 1999 (workshop *Support Tools and Environments*). Je suis également chair dans la conférence EuroPAR'00 qui a eu lieu à Munich en 2000 (workshop *High-Performance Computing and Applications*).

Je fais partie du comité de programme du journal "Parallel and Distributed Computing Practices" <sup>7</sup> dont l'éditeur en chef est Marcin Paprzycki.

#### A.7.5 Relecture pour des journaux et des conférences

J'ai été relecteur pour de nombreuses conférences (EuroPar, IPPS, ICPP, EuroPVM-MPI, PACT, HPCA, STACS, ...) et revues internationales (Parallel Computing, Parallel Processing Letters, Journal of Parallel and Distributed Computing, IEEE Transactions on Parallel and Distributed Computing, Theoretical Computer Science, Journal on Supercomputing, etc.).

#### A.7.6 Groupes de travail ParaMAp

En 1995, j'ai mis en place à Bordeaux le groupe de travail ParaMAp<sup>8</sup> dont le but était, comme pour PA-RAPPLI à Grenoble, de faire se rencontrer les experts du parallélisme et les chercheurs d'autres disciplines ayant besoin de puissance de calcul.

A mon retour en 96, j'ai mis en place le même groupe de travail à l'ENS. Durant l'année 96, nous avons eu 8 exposés autour de thèmes aussi divers que le placement d'antennes radios, les systèmes d'informations géographiques ou l'imagerie médicale. Toutefois, nous avons constaté la difficulté à faire collaborer des chercheurs de disciplines différentes. Nous avons cependant eu quelques succès comme par exemple le stage de Dominique Ponsard que j'ai co-encadré avec G. Vidal du laboratoire des Sciences de la Terre pour la parallélisation avec MPI d'un gros code de Modèle Numérique de Terrain. Ce logiciel a été déposé.

#### A.7.6.1 Suivi des thèses à l'UR Rhône-Alpes

A l'INRIA, j'assure le suivi des thèses effectuées au sein de l'UR. Mon travail consiste à contrôler les dossiers des thèses financées par l'UR, de donner un avis sur certains dossiers, à faire passer les thésards en comité des projets pour des rapports d'avancement, et enfin à effectuer un suivi régulier de toutes les thèses en cours dans l'UR.

$<sup>^6</sup> http://www.ens-lyon.fr/^{\sim} desprez/FILES/RESEARCH/CONF/MSA$

<sup>&</sup>lt;sup>7</sup>http://orca.st.usm.edu/pdcp/

<sup>&</sup>lt;sup>8</sup>Parallélisme Massif et Applications

#### A.7.7 Participation à diverses commissions

Depuis 1999, je fait partie des Commissions de Spécialistes de l'ENS Lyon et de Bordeaux.

Je fais partie du comité de sélection pour la mise en place de la grappe de 200 PCs qui sera installée cette année à l'UR Rhône-Alpes.

#### A.8 Enseignement

J'ai participé à des enseignements depuis le début de ma thèse. Disposant d'une bourse de l'INPG mais effectuant ma thèse à l'ENS Lyon, je n'ai pas pu être moniteur et j'ai donc été vacataire à l'ENS Lyon puis à l'IUT de Valence. Ensuite j'ai été recruté comme ATER à l'ENS Lyon à la fin de ma thèse. Ensuite, au retour de mon postdoctorat, j'ai été recruté comme Maître de Conférences à l'ENSEIRB de Bordeaux où j'ai enseigné dans la filière informatique. Suite à mon recrutement en tant que Chargé de Recherche à l'INRIA, j'ai souhaité continuer cette activité dans divers endroits (comme vacataire). J'ai pu ainsi enseigner en DEA à Lyon, de nouveau à l'ENSEIRB où j'ai été invité à donner un cours en 3ème année et en DESS réseau à Lyon I. J'ai également assuré des formations à Supelec, dans des tutoriaux en France et à l'étranger et dans diverses écoles.

Durant tous ces enseignements, j'ai été amené à suivre des stages d'étudiants de tous niveaux, à rédiger des polycopiés et à participer à l'activité pédagogique à travers des réunions et la mise en place d'options d'enseignement. J'ai également mis en place divers cours comme à l'ENSEIRB (système d'exploitation en 2ème année, parallélisme en 3ème année, équilibrage et régulation de charge en 3ème année) ou en DEA d'informatique fondamentale à Lyon.

#### A.8.1 Cours à l'Université, à l'ENS Lyon et en Ecoles d'ingénieur

#### **2000-2001** CR1 INRIA

• J'ai renoncé cette année à mes cours pour m'occuper à plein temps du projet ReMaP.

#### **1999-2000** CR1 INRIA

- Cours de Recherche Algorithmique Numérique Parallèle au DEA D'Informatique Fondamentale de Lyon (24h de cours, 12 étudiants)

- Cours d'équilibrage et régulation de charge en 3ème année ENSERB à Bordeaux (20h de cours, 12 étudiants)

- Cours et travaux pratiques de MPI en DESS Réseau à Lyon 1 (2h de cours + 9h de TP pour 2 gpes, 40 étudiants)

#### **1998-1999** CR1 INRIA

- Cours et travaux pratique de MPI en DESS Réseau à Lyon 1 (2h de cours + 9h de TPs pour 2 gpes, 40 étudiants)

- Cours d'équilibrage et régulation de charge en 3ème année ENSERB à Bordeaux (20h de cours, 8 étudiants)

#### **1997-1998** CR2-1 INRIA

- Projet d'algorithmique parallèle en Magistère 2ème année à l'ENS de Lyon.

- Cours de Recherche Algorithmique Numérique Parallèle au DEA D'Informatique Fondamentale de Lyon (20h de cours, 8 étudiants)

#### **1996-1997** CR2 INRIA

- Projet d'algorithmique parallèle en Magistère 2ème année à l'ENS de Lyon.

- Cours sur les architectures parallèles dans le cadre du Cours Postgrade en Informatique Numérique de l'Ecole Polytechnique Fédérale de Lausanne (EPFL) (8h de cours, 15 étudiants).

A.8 Enseignement 15

• Cours de Recherche Algorithmique Numérique Parallèle au DEA D'Informatique Fondamentale de Lyon (20h de cours, 10 étudiants)

#### 1995-1996 CR2 INRIA

• Projet d'algorithmique parallèle en Magistère 2ème année à l'ENS de Lyon.

#### 1994-1995

MdC ENSERB: Co-responsable de la 3ème année option parallélisme,

- Parallélisme en 3ème année et DEA : étude et implémentation des algorithmes fondamentaux vus en cours (tris, recherches, algèbre linéaire, ...) avec PVM et HPF (60h de TD/TP, 7 étudiants),

- Systèmes d'exploitation en 2ème année : (Mise en place d'un nouveau cours, des TD et du projet) (30 h de cours, 20h de TD, 48 étudiants),

- Programmation en 1ère année autour du langage C (30h de TD, 25 étudiants),

- Organisation de diverses soutenances de projets pour les trois années,

- Cours de 3h à Besancon (DESS Parallélisme) sur les environnements pour le parallélisme

- Cours de 3h à Nice (3ème année ESSI) sur les bibliothèques de calcul parallèle.

#### **1993-1994** ATER à L'ENS Lyon :

- Système et Logiciel de base en 1ère année de Magistère d'Informatique et Modélisation (Responsabilité du cours, des projets et examens) (32h de cours, 15 étudiants),

- Algorithmique et architectures parallèles en 2ème année de Magistère (Mise en place de nouveaux TD) (32h de TD, 15 étudiants).

#### **1992-1993** Vacataire IUT Valence:

- Algorithmique et langage ADA au département ISI de l'IUT de Valence (96 heures de TP, 70 étudiants),

- DBASE IV et Teamwork (10h de TP, 70 étudiants),

#### 1991-1992

• Permanence programmation pour les magistères 1ère année (ENS Lyon).

#### 1990-1991

- Permanence programmation pour les magistères 1ère année (ENS Lyon).

- Système d'exploitation parallèle (Trollius) présenté aux étudiants de DEA d'informatique de l'ENS Lyon et à des chercheurs de l'école Centrale de Lyon (12h de cours + TP, 20 auditeurs).

- C avancé pour les moniteurs du CIES (16h de cours + TP, 30 étudiants).

#### A.8.2 Cours dispensés à des chercheurs et ingénieurs

• Cours à SUPELEC dans le cadre de la formation continue sur les environnements pour la parallélisation d'applications numériques (*3h de cours, 4 étudiants*).

• Tutorial sur HPF, MPI et OpenMP avec Franck Cappello et Fabien Coehlo à l'Ecole d'hiver iHPerf qui s'est tenue à Aussois en Décembre 2000.

• Cours à SUPELEC dans le cadre de la formation continue sur les environnements pour la parallélisation d'applications numériques (3h de cours, 6 étudiants).

• Cours et travaux pratiques sur MPI dans le cadre du Pôle Scientifique de Modélisation Numérique (PSMN) de Lyon (20h de cours/TPs, 10 auditeurs).

• Tutorial MPI–2–OpenMP avec Luc Giraud (CERFACS) lors de la conférence Euro-PAR'99 (Toulouse, Août 99) (3h, 40 auditeurs).

• Cours à SUPELEC dans le cadre de la formation continue sur les environnements pour la parallélisation d'applications numériques (*3h de cours, 8 étudiants*).

**1996-1997** • Formation TTN ProHPC sur le parallélisme à l'ENS de Lyon

• Tutorial MPI lors d'EuroPAR'97 (Passau, Août 97) (3h de cours, 50 participants)

1995-1996

• Ecole du CNRS sur les outils du parallélisme à l'ENS de Lyon

1994-1995

- Formation MPI lors des Rencontres Francophones du Parallélisme RenPar'7 à Mons (4h de cours) (juin 1995),

- Cours GRECO Informatique avec Bernard Tourancheau "La programmation d'applications scientifiques sur les ordinateurs parallèles à mémoire distribuée" (6h de cours, 20 auditeurs),

- Cours sur les recouvrements calcul/communication dans le cadre d'une journée "Parallélisation automatique et les supports run-time" organisée par Marc Gengler à l'Ecole Polytechnique Fédérale de Lausanne,

- Cours sur les environnements pour la parallélisation de code en milieu industriel lors des Journées Industrielles du Parallélisme (LIP ENS Lyon) (1h30 de cours, 55 auditeurs).

1993-1994

- Cours sur les architectures parallèles avec Michel Cosnard à l'Ecole d'Automne CAPA "Conception et Analyse des Algorithmes Parallèles" (1h30 de cours, 50 auditeurs),

- Formation sur les environnements de programmation pour le parallélisme lors des Rencontres RenPar'6 à Lyon (2h30 de cours, 30 auditeurs),

- Cours et travaux pratiques sur les bibliothèques pour le "Cours Avancé de Calcul Scientifique Parallèle" du Centre Pour le Développement du Calcul Scientifique Parallèle de Lyon I (2h de cours, 5h de TP, 30 auditeurs).

1992-1993

- Cours sur les bibliothèques pour supercalculateurs dans le cadre de la formation des ingénieurs de recherche (ENS Lyon) (2h de cours, 40 auditeurs).

- 1991-1992

- Formations UNIX sur SUN aux chercheurs du laboratoire de mathématiques de l'ENS Lyon (*6h de cours* + *TP, 20 auditeurs*).

#### A.8.3 Responsabilités liées à l'enseignement

J'ai été co-responsable (avec Jean Roman) de la troisième année d'informatique à l'ENSEIRB pour l'année universitaire 94-95.

#### A.9 Publications

#### Livre et chapitres de livres

- [CD94] M. Cosnard and F. Desprez. *Ecole d'Automne CAPA Port d'Albret*, chapter Quelques Architectures de Nouvelles Machines. Hermes, April 1994.

- [DF97] F. Desprez and P. Fraigniaud. *Ordinateurs et Calcul Parallèles*, chapter Les Bibliothèques de Communications, pages 293–312. Number 19 in Arago. OFTA, April 1997.

- [GUD95] M. Gengler, S. Ubéda, and F. Desprez. *Initiation au Parallélisme : Concepts, Architectures et Algorithmes.* Manuels informatiques. Masson, 1995. 2-225-85014-3.

#### Revues internationales avec comité de lecture

- [BBD+99] C. Barberet, L. Brunie, F. Desprez, G. Lebourgeois, R. Namyst, Y. Robert, S. Ubéda, and K. Van Heumen. Technology Transfer within the ProHPC TTN at ENS Lyon. *Future Generation Computer Systems*, 15:309–321, 1999.

- [BCC<sup>+</sup>97a] T. Brandes, S. Chaumette, M.-C. Counilh, A. Darte, J.C. Mignot, F. Desprez, and J. Roman. HP-FIT: A Set of Integrated Tools for the Parallelization of Applications Using High Performance Fortran: Part I: HPFIT and the TransTOOL Environment. *Parallel Computing*, 23(1-2):71–87, 1997.

- [BCC<sup>+</sup>97b] T. Brandes, S. Chaumette, M.-C. Counilh, J.C. Mignot, F. Desprez, and J. Roman. HPFIT: A Set of Integrated Tools for the Parallelization of Applications Using High Performance Fortran: Part II: Data Structures Visualization and HPF Support for Irregular Data Structures with Hierarchical Scheme. *Parallel Computing*, 23(1-2):89–105, 1997.

A.9 Publications 17

[CCCV<sup>+</sup>01] E. Caron, S. Chaumette, S. Contassot-Vivier, F. Desprez, E. Fleury, C. Gomez, M. Goursat, E. Jeannot, D. Lazure, F. Lombard, J.M. Nicod, L. Philippe, M. Quinson, P. Ramet, J. Roman, F. Rubi, S. Steer, F. Suter, and G. Utard. Scilab to Scilab//, the OURAGAN Project. *Parallel Computing*, 2001. to appear.

- [CD01] Frédérique Chaussumier and Frédéric Desprez. Communications Optimizations and Efficient Load-Balancing for a Volume Rendering Algorithm on a Cluster of PCs. *Parallel and Distributed Computing Practices*, 2001. To appear.

- [DDMR96] A. Darte, F. Desprez, J.C. Mignot, and Y. Robert. TransTool: A Restructuring Tool for the Parallelization of Applications Using High Performance Fortran. *Journal of the Brazilian Computer Society*, 3(2):5–15, November 1996.

- [DDP+98] F. Desprez, J.J. Dongarra, A. Petitet, C. Randriamaro, and Y. Robert. Scheduling Block-cyclic Array Redistribution. *IEEE Transaction on Parallel and Distributed Systems*, 9(2):192–205, 1998.

- [DDRR97] F. Desprez, J.J. Dongarra, F. Rastello, and Y. Robert. Determing the Idle Time of a Tiling: New Results. *Journal of Information Science and Engineering (Special Issue on Compiler Techniques for High-Performance Computing)*, 14(1):167–190, March 1997.

- [DDT95] F. Desprez, J.J. Dongarra, and B. Tourancheau. Performance Study of LU Factorization with Low Communication Overhead on Multiprocessors. *Parallel Processing Letters*, 5(2):157–169, 1995.

- [DG95] F. Desprez and M. Garbey. Numerical Simulation of a Combustion Problem on a Paragon Machine. *Parallel Computing*, 21:495–508, 1995.

- [DT94] F. Desprez and B. Tourancheau. LOCCS: Low Overhead Communication and Computation Subroutines. *Future Generation Computer Systems*, 10(2&3):279–284, June 1994.

- [DT95] F. Desprez and B. Tourancheau. Basic Routines for the Rank-2k Update: 2D Torus vs Reconfigurable Network. *Parallel Computing*, 21:353–372, 1995.

#### Revues nationales avec comité de lecture

- [CD94] M. Cosnard and F. Desprez. Quelques Architectures de Nouvelles Machines. *Calculateurs Parallèles*, 21:29–58, March 1994.

- [DGJP93] F. Desprez, C. Gavoille, B. Jargot, and M. Pourzandi. Tests des Performances des Communications de la Machine VOLVOX IS-860. *La Lettre du Transputer et des Calculateurs Parallèles*, 19:11–35, October 1993.

- [DT90] F. Desprez and B. Tourancheau. Modélisation des Performances des Communications sur le Tnode avec le Logical System Transputer Toolset. *La Lettre du Transputer et des Calculateurs Distribués*, 7:65–72, September 1990.

- [DU96] F. Desprez and S. Ubéda. Le Parallélisme dans l'Industrie : Rève ou Réalité? *Technique et Science Informatique*, 15(5):643–647, 1996.

#### Conférences internationales avec comité de lecture et publication des actes

- [BBD+98] C. Barberet, L. Brunie, F. Desprez, G. Lebourgeois, Y. Robert, S. Ubéda, and K. Van Heumen. Technology Transfer within the ProHPC TTN at ENS Lyon. In M. Bubak P. Sloot and B. Hertzberger, editors, *High-Performance Computing and Networking*, LNCS 1401, pages 3–12. Springer Verlag, 1998.

- [BD96a] T. Brandes and F. Desprez. Implementing Pipelined Computation and Communication in an HPF Compiler. In *Europar'96 Parallel Processing*, volume 1123 of *Lecture Notes in Computer Science*, pages 459–462. Springer Verlag, August 1996.

- [BD96b] T. Brandes and F. Desprez. Pipelining Data Parallel Computations in an HPF Compiler. In M. Gerndt, editor, *Sixth Workshop on Compilers for Parallel Computers*, volume 21, pages 73–89, Aachen, Germany, December 1996. Forschungszentrum Jülich.

[BDT93] C. Bonello, F. Desprez, and B. Tourancheau. Parallel BLAS and BLACS for Numerical Algorithms on a Reconfigurable Network. In S. Atkins and A.S. Wagner, editors, *NATUG6* - *Transputer Research and Applications 6*, pages 21–38. IOS Press, 1993.

- [CCD+94] C. Calvin, L. Colombet, F. Desprez, B. Jargot, P. Michallon, B. Tourancheau, and D. Trystram. Towards Mixed Computation Communication in Scientific Libraries. In *CONPAR'94 VAPP VI*, volume 854 of *Lecture Notes in Computer Science*, pages 605–615, Lintz, 1994. Springer Verlag.

- [CD93] C. Calvin and F. Desprez. Minimizing Communication Overhead Using Pipelining for Multi-Dimensional FFT on Distributed Memory Machines. In D.J. Evans, H. Liddell J.R. Joubert, and D. Trystram, editors, *Parallel Computing'93*, pages 65–72. Elsevier Science Publishers B.V. (North-Holland), 1993.

- [CDL99] Frédérique Chaussumier, Frédéric Desprez, and Michel Loi. Efficient Load-Balancing and Communication Overlap in Parallel Shear-Warp Algorithm on a Cluster of PCs. In P. Amestoy, P. Berger, M. Daydé, I. Duff, V. Frayssé, L. Giraud, and D. Ruiz, editors, *Proceedings of EuroPAR'99*, number 1685 in Lecture Notes in Computer Science, pages 570–577, Toulouse, 1999. Springer Verlag.

- [CDP99] Frédérique Chaussumier, Frédéric Desprez, and Loic Prylli. Asynchronous Communications in MPI the BIP/Myrinet Approach. In J. Dongarra, E. Luque, and Tomas Margalef., editors, *Proceedings of the EuroPVM/MPI'99 conference*, number 1697 in Lecture Notes in Computer Science, pages 485–492, Barcelona, Spain, September 1999. Springer Verlag.

- [DD00] F. Desprez and S. Domas. Efficient Pipelining of Level 3 BLAS Routines. In 4th international meeting VECPAR 2000, volume 3, pages 675–688, Porto, June 2000.

- [DDD<sup>+</sup>98] F. Desprez, S. Domas, J. Dongarra, A. Petitet, C. Randriamaro, and Y. Robert. More on Scheduling Block-Cyclic Array Redistribution. In *Proc. of 4th Workshop on Languages, Compilers, and Run-time Systems for Scalable Computers (LCR98)*, volume 1511 of *Lecture Notes in Computer Science*, pages 275–287. Springer-Verlag, Pittsburgh, PA, 1998.

- [DDP+97] Frédéric Desprez, Jack Dongarra, Antoine Petitet, Cyril Randriamaro, and Yves Robert. Block-cyclic Array Redistribution on Networks of Workstations. In M. Bubak, J. Dongarra, and J. Wasniewski, editors, *Recent Advances in Parallel Virtual Machine and Message Passing Interface*, LNCS 1332, pages 343–350. Springer Verlag, 1997.

- [DDP+98] F. Desprez, J. Dongarra, A. Petitet, C. Randriamaro, and Y. Robert. Scheduling Block-Cyclic Array Redistribution. In E.H. D'Hollander, G.R. Joubert, F.J. Peters, and U. Trottenberg, editors, *Parallel Computing : Fundamentals, Applications and New Directions*, pages 227–234. North Holland, 1998.

- [DDPMP96] V. Demian, F. Desprez, H. Paugam-Moisy, and M. Pourzandi. Parallel Implementation of RBF Neural Networks. In *Europar'96 Parallel Processing*, volume 1124 of *Lecture Notes in Computer Science*, pages 243–250. Springer Verlag, August 1996.

- [DDRR97] F. Desprez, J. Dongarra, F. Rastello, and Y. Robert. Determining the Idle Time of a Tiling: New Results. In *Parallel Architectures and Compilation Techniques PACT'97*, pages 307–317, San Francisco, November 1997. IEEE Computer Society Press.

- [DDT96] S. Domas, F. Desprez, and B. Tourancheau. Optimization of the ScaLAPACK LU Factorization Routine Using Communication/Computation Overlap. In *Europar'96 Parallel Processing*, volume 1124 of *Lecture Notes in Computer Science*, pages 3–10. Springer Verlag, August 1996.

- [Des94] F. Desprez. A Library for Coarse Grain Macro-Pipelining in Distributed Memory Architectures. In *IFIP 10.3 Conference on Programming Environments for Massively Parallel Distributed Systems*, pages 365–371. Birkhaeuser Verlag AG, Basel, Switzerland, 1994.

- [DFG<sup>+</sup>99a] F. Desprez, E. Fleury, C. Gomez, S. Steer, and S. Ubéda. Bringing Metacomputing to Scilab. In *Computer Aided Control System Design (CACSD 99)*, Hawaï, USA, August 1999. IEEE.

- [DFG99b] F. Desprez, E. Fleury, and L. Grigori. Scilab//: User interactive application and high performances. In *Third World Multiconference on Systemics, Cybernetics and Informatics (SCI'99) and*

A.9 Publications

- Fifth International Conference on Information Systems Analysis and Synthesis (ISAS'99), Orlando, USA, August 1999. IIIS.

- [DFJ<sup>+</sup>00] F. Desprez, E. Fleury, E. Jeannot, J.-M. Nicod, and F. Suter. Computational servers in a metacomputing environment. In *Parallel Matrix Algorithms and Applications*, Neuchâtel, Switzerland, August 2000. SIAM. to appear.

- [DFT94] F. Desprez, A. Ferreira, and B. Tourancheau. Efficient Communication Operations on Passive Optical Star Networks. In N. J. Davis, editor, *Massively Parallel Processing Using Optical Interconnections*, pages 52–58, Cancun, Mexico, April 1994. IEEE Computer Society Press.

- [DG93] F. Desprez and M. Garbey. Parallel Computing of a Combustion Front. In *Parallel CFD'93 Implementations and Results Using Parallel Computers*. Elsevier Science Publishers B.V., 1993.

- [DP94] F. Desprez and M. Pourzandi. A Comparison of Three Matrix Product Algorithms on the Intel Paragon and Archipel Volvox Machines. In Bl. Sendov I.T.Dimov and P.S.Vassilevski, editors, *Advances in Numerical Methods and Applications NM&A O(h³)′94*, pages 234–244. World Scientific, 1994.

- [DQS01] F. Desprez, M. Quinson, and F. Suter. Dynamic Performance Modeling for Network Enabled Solvers in a Metacomputing Environment. In *International Conference on Parallel and Distributed Processing Techniques and Applications (PDPTA 2001)*, 2001. To appear.

- [DRR96] F. Desprez, P. Ramet, and J. Roman. Optimal Grain Size Computation for Pipelined Algorithms. In *Europar'96 Parallel Processing*, volume 1123 of *Lecture Notes in Computer Science*, pages 165–172. Springer Verlag, August 1996.

- [DS01] F. Desprez and F. Suter. Mixed Parallel Implementations of the Top Level of Strassen and Winograd Matrix Multiplication Algorithms. In *In proceedings of the 15th International Parallel and Distributed Processing Symposium (IPDPS'01)*, San Francisco, April 2001. To appear.

- [DT91] F. Desprez and B. Tourancheau. Reconfiguration versus Static Network in basic scientific routines. In K. Boianov, editor, *Workshop on Parallel and Distributed Processing WP&DP 91*, Sophia, Bulgarie, 1991. Elsevier Science Publishers B.V. (North-Holland).

- [DT92] F. Desprez and B. Tourancheau. A Theoretical Study of Reconfigurability for Basic Communication Algorithms. In L. Bougé, M. Cosnard, Y. Robert, and D. Trystram, editors, *CONPAR* 92 *VAPP V*, volume 634 of *Lecture Notes in Computer Science*, pages 817–818. Springer Verlag, 1992.

#### Conférences internationales avec comité de lecture sans publication des actes

- [DT91a] F. Desprez and B. Tourancheau. Matrix Multiplication and Matrix Transpose : Fixed Topology vs. Switching Network (poster). In *EDMCC2 Munich*, 1991.

- [DT91b] F. Desprez and B. Tourancheau. Reconfiguration versus Fixed Topology. In *European Parallel Computing Action Bonn Workshop*. ESPRIT-PCA Workshop, 1991.

#### Conférences nationales avec comité de lecture sans publication des actes

- [DDP94] F. Desprez, S. Domas, and M. Pourzandi. Comparaison entre 3 Routines de Calcul de Produit de Matrice sur Paragon et Volvox IS-860. In L. Bougé, editor, *Actes des 6es Rencontres Francophones du Parallélisme RenPar'6*, pages 109–118, 1994.

- [Des94] F. Desprez. Recouvrements Calculs/Communications dans les Programmes Scientifiques. In L. Bougé, editor, *Actes des 6es Rencontres Francophones du Parallélisme RenPar'6*, pages 275–279, 1994.

- [DF01] F. Desprez and F.Suter. Produit de matrices, Strassen et parallélisme mixte. In *Treizièmes Rencontres Francophones du Parallélisme*, Paris, La Villette, April 2001.

- [DR00] F. Desprez and C. Randriamaro. Redistribution entre appels de routines ScaLAPACK. In *Actes des* 12èmes Rencontres Francophones du Parallélisme RenPar'00, pages 113–118, Besançon, France, June 2000.

[DZ97] F. Desprez and J. Zory. Performance des Macro-Pipelines dans les Programmes Data-Parallèles. In A. Schiper and D. Trystram, editors, *Actes des 9es Rencontres Francophones du Parallélisme Ren-Par'9*, pages 17–20, Lausanne, Switzerland, May 1997.

#### Rapports de recherches et techniques

- [BCC<sup>+</sup>96] T. Brandes, S. Chaumette, M.-C. Counilh, A. Darte, J.C. Mignot, F. Desprez, and J. Roman. HP-FIT: A Set of Integrated Tools for the Parallelization of Applications Using High Performance Fortran. Technical Report RR-3059, INRIA, December 1996. also LIP ENS Lyon Tech. Rep. 96-28.

- [CDL99] Frédérique Chaussumier, Frédéric Desprez, and Michel Loi. Efficient Load-balancing and Communication Overlap in Parallel Shear-Warp Algorithm on a Cluster of PCs. Technical Report RR1999-28, LIP ENS Lyon, 1999.

- [CDP00] Frédérique Chaussumier, Frédéric Desprez, and Loic Prylli. Asynchronous Communications in MPI the BIP/Myrinet Approach. Technical Report RR-3960, INRIA, 2000.

- [DDD<sup>+</sup>98] Frédéric Desprez, Stéphane Domas, Jack Dongarra, Antoine Petitet, Cyril Randriamaro, and Yves Robert. More on Scheduling Block-Cyclic Array Redistribution. Technical Report 35-24, INRIA, October 1998. Proceedings of LCR'98, LNCS, Springer Verlag and also LIP ENS Lyon Tech. Rep. 98-17.

- [DDP+97] F. Desprez, J.J. Dongarra, A. Petitet, C. Randriamaro, and Y. Robert. Scheduling Block-Cyclic Array Redistribution. Technical Report RR-3117, INRIA, February 1997. also UT CS Dept. Tech. Rep. CS-97-349, LAPACK Working note # 120 and CRPC-TR97714-S.

- [DDPMP96] V. Demian, F. Desprez, H. Paugam-Moisy, and M. Pourzandi. Parallel Implementation of RBF Neural Networks. Technical Report 96-11, LIP ENS Lyon, 1996.

- [DDRR97] F. Desprez, J.J. Dongarra, F. Rastello, and Y. Robert. Determining the Idle Time of a Tiling: New Results. Technical Report 32-72, INRIA, 1997. also LIP ENS Lyon Tech. Report 97-35 and UT CS Dept. Tech. Rep. UT-CS-360.

- [DDT94] F. Desprez, J.J. Dongarra, and B. Tourancheau. Performance Complexity of LU Factorization with Efficient Pipelining and Overlap on a Multiprocessor. Technical Report LAPACK Working Note 67, The University of Tennessee Knoxville USA, 1994.

- [DDT97] F. Desprez, S. Domas, and B. Tourancheau. Optimization of an LU Factorization Routine Using Communication/Computation Overlap. Technical Report RR-3094, INRIA, February 1997. also LIP ENS Lyon Tech. Report 96-17.

- [DFL93] F. Desprez, E. Fleury, and M. Loi. T9000 et C104, La Nouvelle Génération de Transputers. Technical Report 93-01, LIP ENS Lyon, 1993.

- [DFT93a] F. Desprez, A. Ferreira, and B. Tourancheau. Efficient Communication Operations in Reconfigurable Parallel Computers. Technical Report CS-93-209, The University of Tennessee Knox-ville USA, 1993.

- [DFT93b] F. Desprez, P. Fraigniaud, and B. Tourancheau. Successive Broadcast on Hypercube. Technical Report CS-93-210, The University of Tennessee Knoxville USA, 1993.

- [DT92] F. Desprez and B. Tourancheau. LOCCS: Low Overhead Communication and Computation Subroutines. Technical Report 92-44, LIP ENS Lyon, December 1992.

#### Mémoires

- [Des90] F. Desprez. Algèbre Linéaire sur TNode. Master's thesis, Ecole Normale Supérieure de Lyon, June 1990. Laboratoire LIP.

- [Des94] F. Desprez. *Procédures de Base pour le Calcul Scientifique sur Machines Parallèles à Mémoire Distribuée.* PhD thesis, Institut National Polytechnique de Grenoble, January 1994. LIP ENS-Lyon.

# Optimization of a LU Factorization Routine Using Communication/Computation Overlap

**Conference**: EuroPAR

**Date:** 1996

Authors:

F. Desprez, S. Domas and B. Tourancheau LIP, CNRS URA 1398, INRIA Rhône-Alpes Ecole Normale Supérieure de Lyon 46, Allée d'Italie 69364 LYON cedex 07 (desprez, sdomas, btouranc)@lip.ens-lyon.fr

#### Abstract:

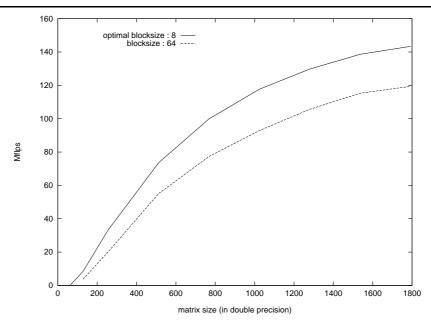

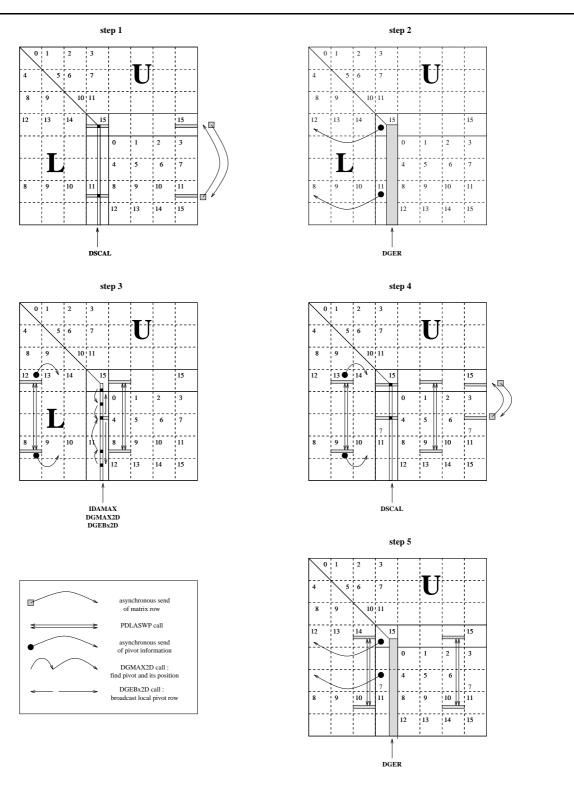

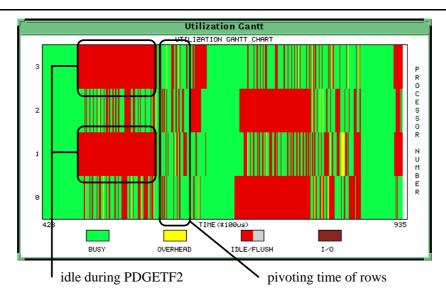

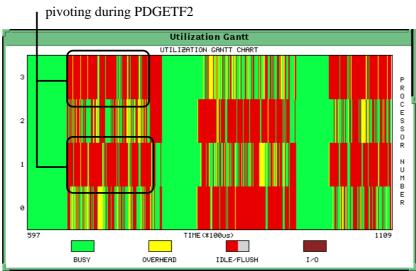

This paper presents some works on the *LU* factorization from the ScaLAPACK library. First, a complexity analysis is given. It allows to compute the optimal block size for the block scattered distribution used in ScaLAPACK *LU*. It also gives the communication phases that are interesting to overlap. Second, two optimizations based on computations/communications overlap are given with experimental results on Intel Paragon system and IBM SP2 system.

#### Keywords:

Parallel numerical libraries, overlap of commications, pipelining, ScaLAPACK.

#### Thanks:

This work has been supported by the INRIA Rhône-Alpes and the EUREKA-EUROTOPS project. We thank the CDCSP of the University Claude Bernard Lyon I, France, for providing the access to their Intel Paragon machine.

#### **B.1** Introduction

The LU factorization is the kernel of many applications. Thus, the importance of optimizing this routine has not to be proven because of the increasing demand of applications dealing with large matrices. Its efficient parallel implementation can bring real improvements in the execution speed of the whole application. The speed-up depends greatly on the kind of supercomputer chosen. Vector machines have very high performances, but a prohibitive cost. Distributed memory machines seem to be a good balance between performances and cost.

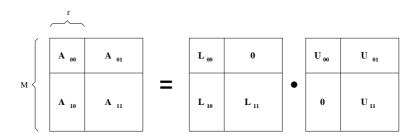

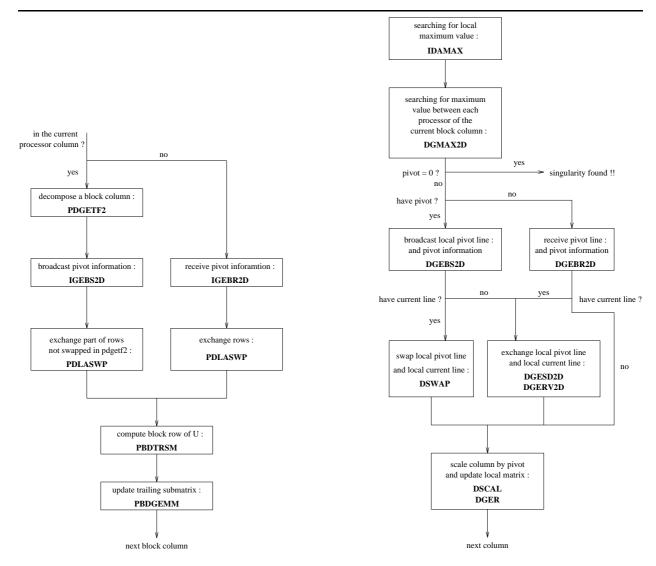

Portability is one of the key issue of computer programming. Many libraries have been designed to ensure portability and performances across multiple architectures. The BLAS [4, 5, 10] and LAPACK [6] are available on many platforms, provided by computers vendors. LU factorization was released in the LAPACK package, using levels 1, 2 and 3 BLAS. ScaLAPACK [1] is the parallel version of a subset of LAPACK. ScaLAPACK has been designed to ensure portability, performances and ease of use across many parallel machines. Matrices are distributed in a block scattered way. Parallelism is hidden in a parallel version of the BLAS called PBLAS [25]. Communications between processors on a virtual grid are done using the BLACS package [7].

The aim of this paper is to show that improvements can be obtained in the existing ScaLAPACK *LU* factorization routine by the use of overlap techniques.